### DESIGN, CONSTRUCTION AND ANALYSIS OF A SINGLE PHASE INVERTER

By

### M. SADDAM HOSSAIN KHAN

#### MASHFIQUL ISLAM

#### **MD. ISTIANATUR RAHMAN**

Submitted to

#### The Department of Electrical and Electronic Engineering

#### **Faculty of Science and Engineering**

East West University

In partial fulfillment of the requirements for The degree Of Bachelor of Science in Electrical & Electronics Engineering

(B.Sc. in EEE)

Spring, 2011

Thesis Supervisor:

Dr. Shahidul Islam Khan

Chairperson:

Dr. Anisul Haque

# ABSTRACT

A single phase inverter is designed and constructed to provide regulated output voltage at 220V. The output power stage is designed in two methods first one is using four power transformers in H-bridge mode to the load through a transformer, and another one is two NMOS power transistors coupled to the load through a transformer. The output is a 50Hz square wave which is obtained by totem-pole driver operation of two transistors using 50 Hz complementary trigger pulse stream for first method. And for the second method 50Hz square wave is obtained using a single PNP transistor. The inverter is constructed and presented. The circuit is tested and it is found that the waveforms obtained at different stages of the circuit conform well to those obtained by computer simulation. The inverter circuit is found to be efficient for applications in appliances.

# ACKNOWLEDGEMENTS

**Dr.** Shahidul Islam Khan, Professor of the Department of Electrical and Electronic Engineering, BUET for his valuable guidance, constant encouragement, and whole hearted supervision throughout the progress of our work, without which this project would have never been materialized.

we also express our sincere gratitude to Mr. Shafayetur Rahman, Technical Officer for all the guidance he provided to us during the construction of the hardware.

We also thank Dr. Anisul Haque, Chairperson, Department of Electrical and Electronic Engineering, East West University and Mr. Mahmudur Rahman Siddiqui, Research Lecturer, Department of Electrical and Electronic Engineering, East West University for their valuable suggestions and help.

Finally, we express our utmost gratitude to all our friends and family members for the valuable discussions we shared in the course of this project.

## APPROVAL

The project titled 'Design, construction and analysis of a single phase inverter' submitted by M. Saddam Hossain Khan (2007-2-80-011), Mashfiqul Islam (2007-2-80-012) and Md. Initianatur Rahman (2007-2-80-015), has been accepted as satisfactory in partial fulfillment of the requirements for the degree of Bachelor in Science in Electrical and Electronic Engineering on April 2011.

2011

(Supervisor)

Professor

Department of Electrical and Electronic Engineering,

BUET. Dhaka.

Dr. Shahidul Islam Khan

# AUTHORIZATION

We hereby declare that we are the sole authors of this thesis and it has not been submitted elsewhere for the award of any degree or diploma. We authorize East West University to lend this thesis to other institutions or individual on request for the purpose of scholarly research only.

We further authorize East West University to reproduce this thesis by photocopy or other means in total or in part at the request of other institutions or individuals for the purpose of scholarly research only.

Countersigned

Signature of the students

Dr. Shahidul Islam Khan

(Supervisor)

Saddamfossainkhan

M. Saddam Hossain Khan

Mislan

Mashfiqul Islam

MD. ISTIANATUR RAHMAN

Md. Istianatur Rahman

### Contents

| Abstract                                                     |

|--------------------------------------------------------------|

| Acceswledgement                                              |

| Approval                                                     |

| Authorization                                                |

| Contents                                                     |

| List of Figures                                              |

| <b>CHAPTER 1: INTRODUCTION</b>                               |

| L1 Introduction                                              |

| 12 Different types of Inverter                               |

| 13 The Proposed Method                                       |

| 14 Scope of the Project                                      |

| 15 Introduction to the Chapters                              |

| CHAPTER 2: PRINCIPLE OF OPERATION AND COMPUTER SIMULATION OF |

| PROPOSED METHOD                                              |

| 2.1 Introduction                                             |

| 2.2 Principle of Operation                                   |

| Deration of a Single Phase Half Bridge Inverter              |

| 2.3 Operation of a Single Phase full Bridge Inverter         |

| 2.4 Modulation Technique                                     |

| 2.5 Computer Simulations                                     |

| 2.5.1 Introduction                                           |

| 2.5.2 Simulated Outputs                                      |

| 2.6 Summary                                                  |

| <b>CHAPTER 3: DESIGN CONSTRUCTION AND ANALYSIS</b>           |

| 3.3 Introduction                                             |

| 32 Functional Description of the Inverter                    |

| 3.3 Functional Description of parameters in Internal Blocks  |

| 3.3.2 Introduction to Power MOSFET                           |

| 3.3.2.1 IRF Z44 N Channel MOSFET                             |

| 3.3.2.2 IRF9520 P channel MOSFET                             |

| 3.3.3 Driver circuit                                         |

| 33.4 Optocoupler (4N35)                                   |

|-----------------------------------------------------------|

| 34 Design Criteria                                        |

| 341 Design of the Driver Stage                            |

| 3.4.1.1 Driver circuit for N channel MOSFET               |

| 3.4.1.2 Driver circuit for P channel MOSFET               |

| 3.4.2 Design of the 50 Hz Antiphase Square wave Generator |

| 3.4.3 Design of the power output stage                    |

| 3.4.4       Total Harmonic Distortion (THD) analysis      |

| 3.4.5 Selection of the output Transformer                 |

| 3.4.6 Design of the Feed Back Stage                       |

| 35 Construction and Testing                               |

| 3.5.1 Construction                                        |

|                                                           |

| 3.5.2 Testing                                             |

| 3.5.2.1 Output Wave shape of Square wave Generator        |

| 3.5.2.2 Voltage Wave shapes of transformer Primary        |

| 3.5.2.3 Constructed Single Phase Inverter                 |

| 3.6 Analysis                                              |

| 3.7 Conclusion                                            |

| <b>CHAPTER 4: TECHNIQUE OF IMPROVEMENT IN EFFICIENCY</b>  |

| 4.1 Introduction                                          |

| 42 Proposed Technique for Improved Efficiency             |

| 43 Implementation and Outcome                             |

| 4.4 Conclusion                                            |

| <b>CHAPTER 5: SUMMARY CONCLUSION AND RECOMMENDATION</b>   |

| 50 Semmary 72                                             |

| 51  | Summary                     | 72  |

|-----|-----------------------------|-----|

| 52  | Conclusion.                 | 72  |

| 53  | Suggestions for Future Work | 72  |

| Ref | erence                      | .73 |

#### List of Figures:

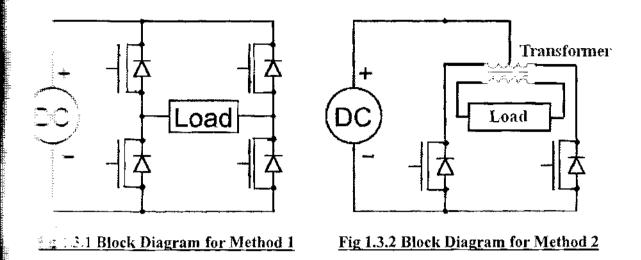

- Block Diagram for Method 1

- Block Diagram for Method 2

- Block Diagram of Half Bridge

- Voltage Waveform of Half Bridge

- Voltage Waveform

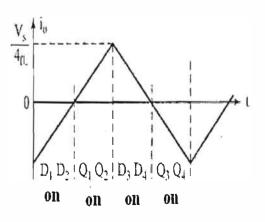

- Current Waveform

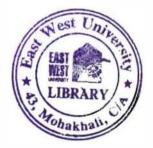

- Figure of less than 50% duty cycle that is efficient for transistor action.

- Figure of 50% duty cycle that is harmful for transistor action.

- Single Pulse Width Modulation

- Harmonic contents of Single Pulse Width Modulation

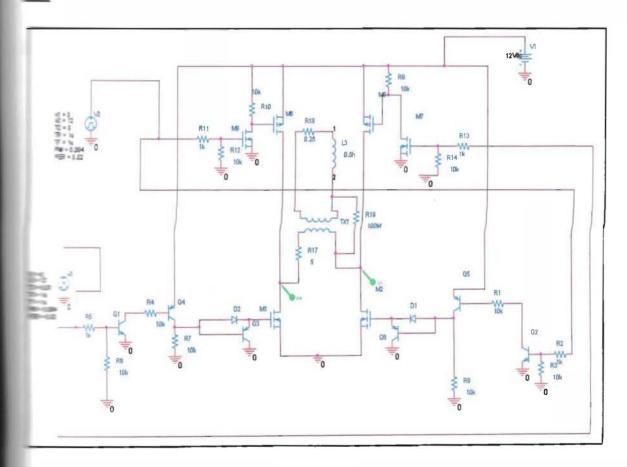

- Schematic Diagram of Single Phase Full Bridge Inverter with Highly Inductive Load

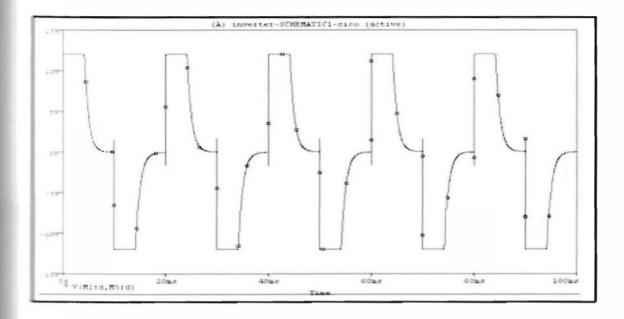

- Output voltage of a single phase full bridge inverter with highly inductive load for 20% duty cycle

- Output voltage of a single phase full bridge inverter with highly inductive load for 20% duty cycle

- Harmonic Distortion for 20% duty cycle

- Output voltage of a single phase full bridge inverter with highly inductive load for 30% duty cycle

- Harmonic distortion for 30% duty cycle

- Output current of a single phase full bridge inverter with highly inductive load

- 25.2(h) Output current of a single phase full bridge inverter with highly inductive load

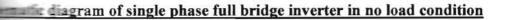

- Schematic diagram of single phase full bridge inverter in no load condition

| 2.5.2(j)    | Output voltage of a single phase full bridge inverter in no load condition                 |

|-------------|--------------------------------------------------------------------------------------------|

| 2.5.2(k)    | Output voltage of a single phase full bridge inverter in no load condition                 |

| 2.5.2(l)    | Schematic diagram of single phase full bridge inverter with transformer and inductive load |

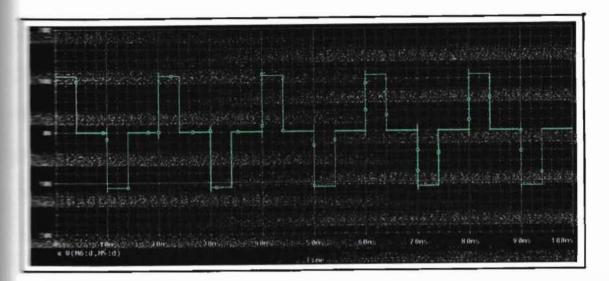

| 2.5.2(m)    | Primary side output voltage of single phase full bridge inverter with inductive load       |

| 2.5.2(n)    | Schematic diagram of single phase full bridge inverter with transformer and inductive load |

| 2.5.2(o)    | Primary side output voltage of single phase full bridge inverter with inductive Load       |

| 3.2(a)      | Block diagram of the inverter                                                              |

| 3.2(b)      | Schematic diagram of the inverter in method 1                                              |

| 3.2(c)      | Schematic diagram of the inverter in method 2                                              |

| 3.2(d)      | Schematic Diagram of MOS Protection, Filter and Snubber circuit                            |

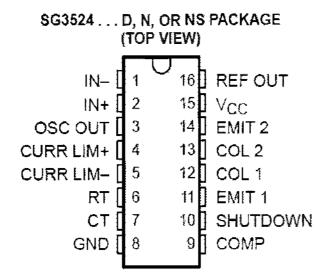

| 3.3.1(a)    | Top view of SG3524                                                                         |

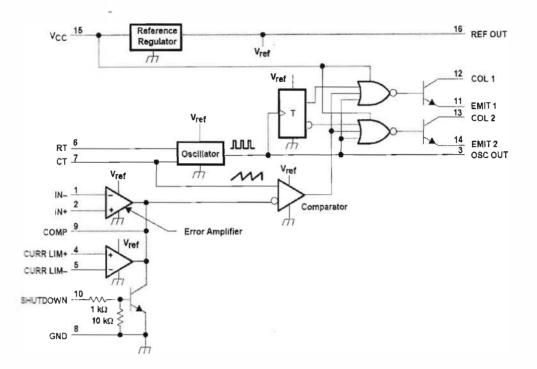

| 3.3.1(b)    | Functional Block Diagram of SG3524                                                         |

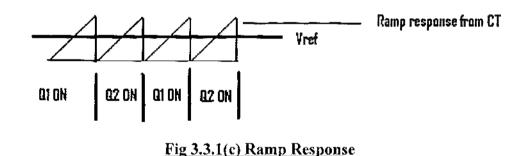

| 3.3.1(c)    | Ramp Response                                                                              |

| 3.3.2 (a)   | Power MOSFET                                                                               |

| 3.3.2 (b)   | Power MOSFET symbol                                                                        |

| 3.3.2(c):   | I-V characteristics of power MOSFET.                                                       |

| 3.3.2(d)    | Avalanche mode Curve                                                                       |

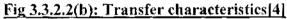

| 3.3.2.1(a): | I-V characteristics                                                                        |

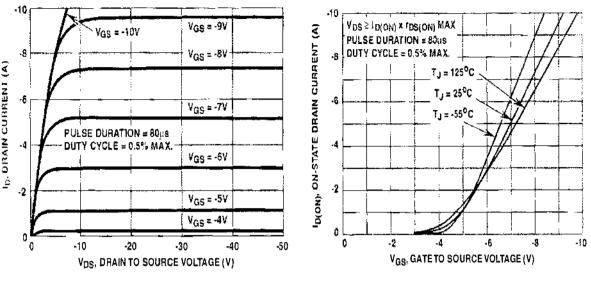

| 3.3.2.1(b): | Transfer characteristics                                                                   |

| 33.7.2(a): | I-V characteristics                                             |

|------------|-----------------------------------------------------------------|

| 3322(b):   | Transfer characteristics                                        |

| 3.3.3(a)   | Power MOSFET gate driver                                        |

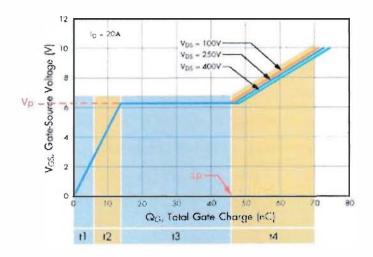

| 3.3.3(b)   | Gate Charge vs Vgs of a Power MOSFET                            |

| 3.3.4(a)   | Optocoupler                                                     |

| 3.4.1.1(a) | Schematic Diagram of N Channel MOSFET Driver for method 1       |

| 3.4.1.1(b) | Schematic Diagram for N Channel MOSFET Driver for method 2      |

| 3.4.1.2(b) | Schematic diagram of driver and power output stage              |

| 3.4.2(a)   | Schematic diagram of the frequency generator stage              |

| 3.4.3(a)   | Schematic diagram of the power output stage                     |

| 3.4.6      | Feedback Stage                                                  |

| 35.2.1(a)  | Square Wave Generation from SG3524                              |

| 3.5.2.2(a) | Voltage Wave shape at Primary at No Load Condition for Method 1 |

| 3.5.2.2(b) | Voltage Wave shape at Primary at No Load Condition for Method 2 |

| 3.5.2.2(c) | Voltage Wave shape at Primary at 60W Load for Method 2          |

| 3.5.2.3(a) | Inverter Hardware                                               |

| 3.5.2.3(b) | Inverter with 5W load                                           |

| 3.5.2.3(c) | Inverter with 60W load                                          |

| 3.5.2.3(d) | Primary no load wave shape                                      |

10

### List of Tables:

Switching states of Full Bridge Inverter

Power Stage Analysis

### CHAPTER 1 INTRODUCTION

#### L1 Introduction

The supply ac voltage at fixed voltage and frequency. However, there are many monotonic where variable voltage and frequency are required. Inverter is equipment that input dc voltage to variable frequency and variable amplitude ac voltage. One of the monotonic application of inverter is variable speed ac drives, where input ac is made variable frequency and amplitude) by rectifier-inverter configuration.

The output voltage waveforms of ideal inverter should be sinusoidal and contain certain monoics. For low and medium power applications, square wave or quasi square wave may be acceptable; and for high power applications, low distorted sinusoidal mediums are required.

inverter applications, it is necessary to be able to control both the output voltage and output frequency. The controllable voltage requirement may arise out of the need to regulation in the connected ac equipment or to maintain constant flux in ac motors variable speed by variation of their supply frequency. If the dc input voltage is the lable, then an inverter with a fixed ratio of dc input voltage may be satisfactory. If the voltage is not controllable, then the control of output voltage must be obtained by many pulse width modulation.

#### some applications of inverters are:

- Stand-by power supplies.

- Induction heating.

- Variable ac motor drives.

- Uninterruptable power supplies for computers.

- Aircraft power supplies.

- Output of de transmission lines.

- Air conditioning.

#### : Different types of Inverter

- Single phase inverter

- Three phase inverter

- Poly phase inverter

- High voltage inverter

- Multi-level inverter

- Voltage source inverter

- Current source inverter

#### The Proposed Method

ale phase square wave is used as switching function to operate the proposed single

a inverter. Transistors are used as switches. The triggering of these switching devices is

bed from two complement square waves and by a feedback loop from output to the This produces closed loop control which maintains constant output voltage under

a load conditions.

analysise implementation, we are proposing two methods.

The MOSFETs are used. The NMOS are used for negative switching and the PMOS are positive switching which enables more efficiency and lesser voltage drop in the defined are switching.

The set 2. the proposed inverter is basically a push-pull arrangement which is a full bridge where the negative switching is done using two N type MOSFETs and the positive as a somected directly to the transformer at the load. This enables to minimize the power station as there is no switching involved in the positive side.

the survey at the output.

#### Sope of the Project

Load, it is difficult to keep the output voltage constant. The scope and objective of this of its to maintain the constant output voltage at different loads and also to increase the output of the inverter i.e. get the maximum voltage at the output node with minimum loss may switching.

#### 15 Introduction to the Chapters

The contents of this project have been organized as follows:

2, the principle of operation of a single phase half bridge inverter and a full bridge inverter and a full bridge inverter is discussed. The modulation technique used and the computer simulated outputs of inverter are shown n discussed in this chapter as well.

design, construction and analysis of the proposed inverter are discussed in Chapter 3. functional description of the two methods used, the PWM square wave generation using 24 and all the other devices and parts used in the construction is individually discussed this chapter. The details of design, construction and testing are also discussed.

The technique of improving the efficiency of the proposed inverter and the analysis of the efficiency is discussed in Chapter 4.

The presents the conclusion, summary of the whole paper and the future improvements the proposed inverter.

## CHAPTER 2 PRINCIPLE OF OPERATION AND COMPUTER SIMULATION FOR PROPOSED METHOD

#### **Introduction**

bridge inverter with mathematical analysis are discussed. Fourier series is used for matical analysis. The input current of a single-phase inverter is also analyzed.

#### Principle of Operation

The operations of single phase half and full bridge inverters are discussed in the following descriptions:

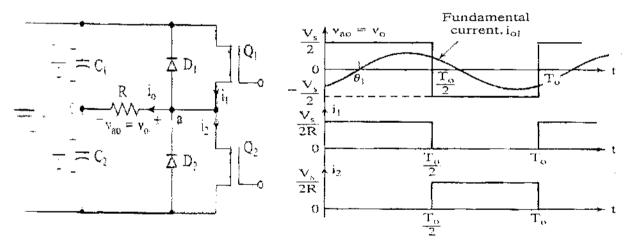

#### Operation of a Single Phase Half Bridge Inverter

principle operation of a single-phase half bridge inverter can be explained with the help given figure. The inverter consists of two choppers. When only transistor  $Q_1$  is turned for a time  $T_0/2$ , the instantaneous voltage across the load  $v_0$  is  $V_s/2$ . If only transistor  $Q_2$  is on for a time  $T_0/2$ ,  $-V_s/2$  appears across the load. The logic circuit has to be designed a way that  $Q_1 \& Q_2$  are not turned on at simultaneously. Figure 2.2.b shows the for the output voltage and transistor currents with the resistive load. This inverter three-wire dc source, and when transistor  $Q_2$  is off, its reverse voltage instead of This inverter is known as a half wave bridge inverter. and square (rms) output voltage can be found from

$$\frac{1}{1} \frac{1}{1} \frac{1}{1} \frac{V_s^2}{4} dt = V_s/2 \dots \dots (i)$$

in the series as the expressed in Fourier series as

$$\frac{2\pi}{2} \sum_{n=1}^{\infty} (ancos(n\omega t) + bnsin(n\omega t)) \dots \dots \dots \dots (ii)$$

$a_{n}$  and  $a_{n}$  are zero. We get  $b_{n}$  as

$$\int_{-\frac{1}{2}}^{\frac{1}{2}} \frac{d(\omega t)}{2} + \int_{0}^{\frac{\pi}{2}} \frac{V_s}{2} d(\omega t) = \frac{4V_s}{n\pi}$$

......(iii)

the instantaneous output voltage Vo as

$$= \sum_{n=1}^{\infty} \frac{2Vs}{n\pi} sin(n\omega t)) \dots \dots \dots (iv)$$

Block Diagram of Half Bridge

Fig: 2.2.1(b) Voltage Waveform

The internet cannot change immediately with output voltage for an inductive load. When

The internet cannot change immediately with output voltage for an inductive load. When

The internet fails to zero. Similarly when Q2 turned off at T0 the load current

The internet fails to zero. Similarly when Q2 turned off at T0 the load current

The internet fails to zero. Similarly when Q2 turned off at T0 the load current

The internet fails to zero. Similarly when Q2 turned off at T0 the load current

The internet fails to zero. Similarly when Q2 turned off at T0 the load current

The internet fails to zero. Similarly when Q2 turned off at T0 the load current

The internet fails to zero. Similarly when Q2 turned off at T0 the load current

The internet fails to zero. Similarly when Q2 turned off at T0 the load current

The internet fails to zero. Similarly when Q2 turned off at T0 the load current

The internet fails to zero. Similarly when Q2 turned off at T0 the load current

The internet fails to zero. Similarly when Q2 turned off at T0 the load current

The internet fails to zero. Th

211(c) Voltage waveform

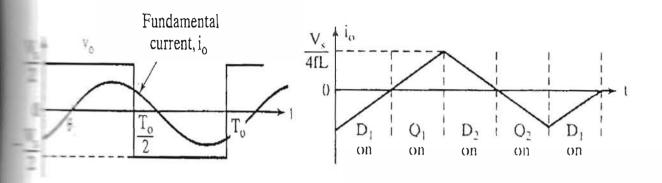

#### Fig 2.1.1(d) Current Waveform

The purely inductive load each of the transistors conducts only for T0/2. Depending upon the second second

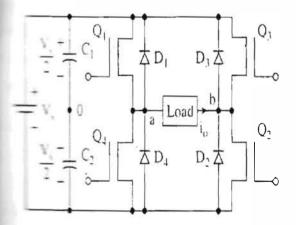

#### Operation of a Single Phase full Bridge Inverter

2.1a. A single-phase full bridge inverter can be explained with the help 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full bridge inverter consists of 4 choppers Q1 Q2 Q3 & Q4. 2.1a. A single-phase full br

**Block Diagram of Full Bridge**

come output can be found from

$$= G_{0}^{\frac{2}{5}} \int_{0}^{To/2} \frac{v_{s}^{2}}{4} dt \, t^{1/2} = \text{Vs} \dots \dots \dots (v)$$

maneous voltage can be expressed in Fourier series as

sing table shows the switching states for full bridge inverter

| -                                             | State<br>No | Switch<br>State | Va0           | Vb0            | V0        | Component Conducting                    |

|-----------------------------------------------|-------------|-----------------|---------------|----------------|-----------|-----------------------------------------|

| StatS<br>and State<br>StatS<br>and S          | I           | 10              | Vs/2          | -Vs/2          | Vs        | S1 and S2 if i0>0<br>D1 and D2 if i0<0. |

| > and S3<br>are 7% and<br>S and S2<br>are 0FF | 2           | 01              | -Vs/2         | Vs/2           | -Vs       | D4 and D3 if i0>0.<br>S4 and S3 if i0<0 |

| StatS<br>million<br>StatS<br>million<br>F     | 3           | 11              | Vs/2          | Vs/2           | 0         | S1 and D3 if i0>0.<br>D1 and S3 if i0<0 |

| StatS<br>and<br>StatS<br>and<br>StatS         | 4           | 00              | -Vs/2         | -Vs/2          | 0         | D4 and S2 if i0>0.<br>S4 and D2 if i0<0 |

| Sin 4<br>ball<br>Ball<br>Ball<br>B            | 5           | OFF             | -Vs/2<br>Vs/2 | -Vs/2<br>-Vs/2 | -Vs<br>Vs | D4 and D3 if i0>0.<br>D1 and D2 if i0<0 |

### Table 2.2.2(a) Switching states of Full Bridge Inverter

transistor sign Q is replaced with S.

#### - \* Modulation Technique

The state of a high-frequency signal in order to obtain the modulated signal. In most of the cases, the state signal is a high-frequency signal in order to obtain the modulated signal. In most of the cases, the state signal is a high-frequency sinusoid waveform. However, a square wave pulse train is also a state state [13].

the twenter gain can be varied following multiple techniques the most efficient method of which is to the gain and output voltage and to incorporate pulse width modulation (PWM) control within the effect. Pulse-width modulation (PWM) is used to control power which is then used as input to the effect devices. Turning the switch between supply and load on and off at a fast pace the affect average value of voltage (and current) fed to the load, and this would not have been affect althout the help of modern switches. The time length for which the switch is left on is the as the magnitude of the power supply to the load. The PWM switching frequency has to be the faster to have an effect on the device that uses the power. Observations suggest switching have the time several times a minute in an electric stove, 120 Hz in a lamp dimmer, from few kilohertz that so is kHz for a motor drive and well into the tens or hundreds of kHz in audio amplifiers to the power supplies[14].

The main advantages of PWM is that it brings down the power loss in the switching devices. In the main advantages of PWM is that it brings down the power loss in the switching devices. In the mode, it barely allows any flow of current and there is almost no voltage drop across the set it is on. This signifies that the power loss in insignificant as it results from the product of the set is current, both of which has near zero values in both on and off states. PWM is more than the set is with digital controls because they can easily set the needed duty cycle (duty cycle being the set in of 'on' time to the regular interval or 'period' of time); low power succeeds a low duty to the set is a succeeds a low duty the set is a succeed by the set is a set is

#### Fig 2.4(a) figure of 50% duty cycle that is harmful for transistor action.

Santania k

Statute.

321424 ...

<u>2.4.b) figure of less than 50% duty cycle that is efficient for transistor action.</u>

mmonly used techniques are [16]:

- Single-pulse-width modulation

- Multiple-pulse-width modulation

- Sinusoidal pulse-width modulation

- Modified sinusoidal pulse-width modulation

- Phase displacement control

- Hysteresis (Bang-bang) pulse-width modulation

- Space Vector pulse-width modulation

The switching functions for the analysis and implementation of the inverter are brought about by a ingle pulse modulation. The single-pulse-width modulation technique is discussed on the later part [14].

#### gle pulse width modulation

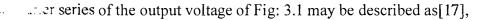

**be** gating signals are generated by comparing a rectangular reference signal of amplitude with a triangular carrier wave of amplitude Ac. The frequency of the carrier wave mermines the fundamental frequency of the output voltage. By varying Ar from 0 to Ac, the width ' $\delta$ ' can be varied from 0 to 180. The ratio of Ar to Ac is the control variable and fined as the modulation index [15].

me modulation index,

**M= Ar/Ac** ..... (vii)

me mus output can be found from

$$V_{0} = \left[ \frac{2}{2\pi} \int_{(\pi-\delta)/2}^{(\pi+\delta)/2} V S^{2} d(\omega t) \right]^{\frac{1}{2}}$$

$$= V_{s} \sqrt{\delta/\pi} \dots (viii)$$

Fig 2.4.1 Single Pulse Width Modulation [19]

### $= 2\pi \int_0^{\pi} Vs \cos(n\omega t) d(\omega t)$

=

$$\lim_{\pi} \int_{(\pi-\delta)/2}^{(\pi+\delta)/2} \cos(\pi\omega t) d(\omega t) = 0$$

.....(xi)

Equation 3.1 becomes,

###

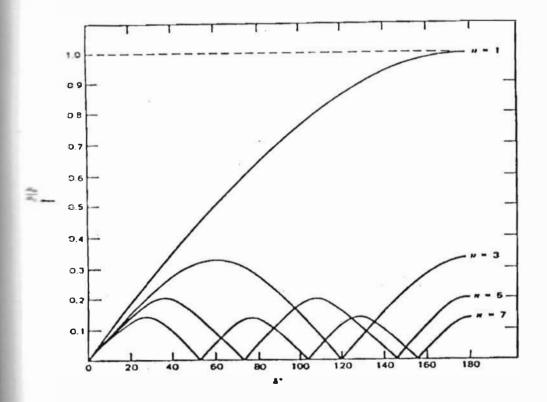

these curves it may be seen that as ' $\delta$ ' is decreased, the harmonic content of the output object waveform increases until, when the amplitude of the fundamental component has reduced to 20% of its maximum value, the amplitude of the three harmonics illustrated means nearly equal to that of the fundamental[17].

Fig 2.4.2 Harmonic contents of Single Pulse Width Modulation[19]

#### 2.5 Computer Simulations

#### <u>Introduction</u>

the software ORCAD. ORCAD is electronic design automation software. It is usually construct electronic schematics and diagrams for simulation purpose. Using this were, the simulation of the whole inverter circuit with load and without load has been two that the values of designed parameter can be obtained for hardware implementation.

#### . 51 Simulated Outputs

#### • method 1

#### matic diagram of Single phase full bridge inverter with highly inductive load

Fig 2.5.2(a)

where the stage of a single phase full bridge inverter with highly inductive load for 20%

ant cycle

Fig 2.5.2(b)

#### monaic distortion for 20% duty cycle

<u>Desput voltage of a single phase full bridge inverter with highly inductive load for 30%</u> <u>evcle</u>

Fig 2.5.2(e)

#### menic distortion for 30% duty cycle

| 이 사실에 있는 것은 것을 가지 않는 것을 다 있는 것을 다 있는 것을 다 있는 것을 해야 한다. 것은 것은 것은 것은 것은 것은 것을 가지 않는 것을 하는 것을 하는 것을 하는 것을 하는 것을 다 가 가 있는 것을 다 나는 것을 다 가 있는 것을 다 가 있는 것을 다 나는 것을 다 가 있는 것을 다 가 있 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                            |

| and the second secon                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                            |

| 1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.                                                                                                                                                                                                                                                                                                                                     |

| 106/// 206// 306// NOR/// OK/// OK/// OK/// 206/// 206/// 206/// 206///                                                                                                                                                                                                                                                                                                    |

| a #(#2#:1,L4:2)                                                                                                                                                                                                                                                                                                                                                            |

| Frequency                                                                                                                                                                                                                                                                                                                                                                  |

Fig 2.5.2(f)

manut current of a single phase full bridge inverter with highly inductive load

and the second the Breaked plant in the 50ms 69ms 70ms 80ms 90ms 100ms 3 des 20m

Fig 2.5.2(g)

Fig 2.5.2(h)

tic diagram of single phase full bridge inverter in no load condition

Fig 2.5.2(i)

sent subage of a single phase full bridge inverter in no load condition

Fig 2.5.2(j)

Fig 2.5.2(i)

betreat voltage of a single phase full bridge inverter in no load condition

Fig 2.5.2(j)

Fig 2.5.2(k)

# Sedematic diagram of single phase full bridge inverter with transformer and inductive

Fig 2.5.2(1)

Fig 2.5.2(m)

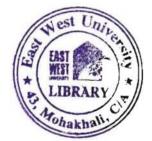

#### method 2

# state and inductive and inductive

Fig 2.5.2(n)

side output voltage of single phase inverter with inductive load

Fig 2.5.2(0)

#### manic distortion for 20% duty cycle:

#### Summary

in principle of operation of a single phase inverter and computer analysis of output voltage input current (with load and without load) for both the two methods is discussed and in this chapter. The output voltage will contain only fundamental frequency if all the harmonics are filtered out.

theoretical analysis is demonstrated by the computer analysis and the computer simulated are analogous to the actual input, output waveforms.

### CHAPTER 3 DESIGN, CONSTRUCTION AND ANALYSIS

#### 3.1 Introduction

In this chapter, the implementation of the proposed method for single phase full bridge inverter has been discussed. A proper design gives an accurate result. There are many switching devices available to switch on and off in a particular circuit. The important task is to choose suitable devices considering data like power loss, power rating, efficiency etc.

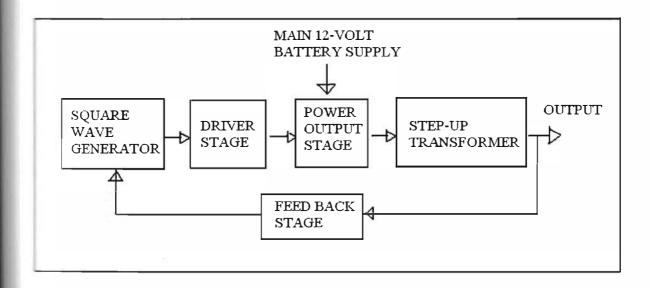

#### **Eunctional Description of the Inverter**

#### Fig 3.2(a) Block diagram of the inverter

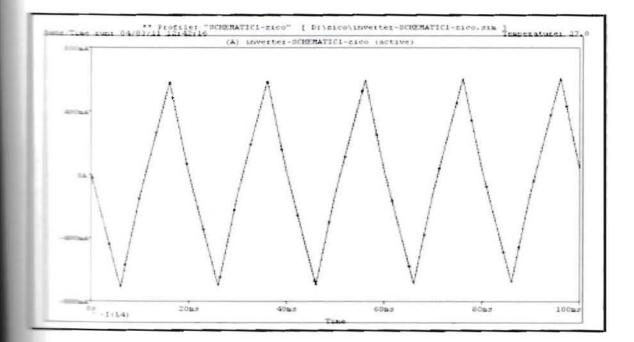

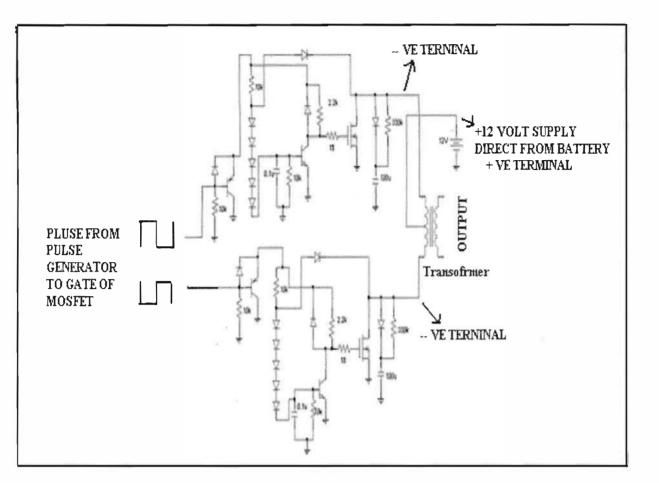

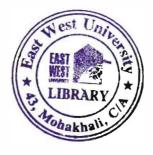

#### For method 1

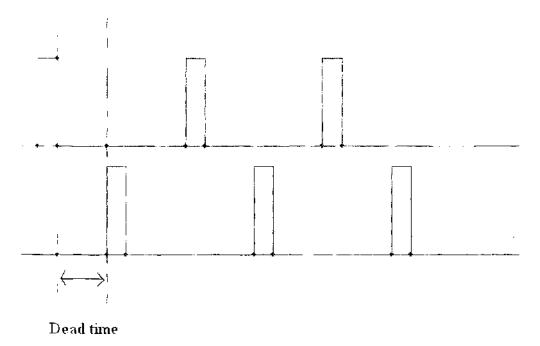

main motive is to supply a 12 volts dc input and obtained a 220 volts Ac output across load. For that, H-bridge method has been followed. The 12 volts has been supplied from a mery which supplies constant 12 volts dc. At first, 50Hz pulse has been generated using SG3524 pulse generator .SG3524 is an anti-square wave generator which has two outputs. 180 degree shifted pulse can be obtained from two different outputs. Then, those pulses of amplitude 12 volts were given to the gate of the MOSFETs which were used as switches. Two NMOS and two PMOS have been used for the switching purpose. The PMOS has been used in the high side switching or during positive switching and the NMOS has been used in the low side switching or during negative switching. The MOSFETs here conduct in pairs. As one NMOS and one PMOS conduct as a pairs so we have two pairs here. The gate of each pair has been given to two pairs for conduction. When positive pulse appears at the gate of the MOSFETs, they turn ON and during the appearance of negative pulse they remain OFF. While positive pulse from one output appears to the gate of one pair, they turn ON but at the same time the other pair remains OFF because negative pulse from another output appears at the gate of other pair as anti-square wave has been generated from two outputs. SG3524 has been designed in such a way that it generates the pulses with **dead time calculation**. So, there is no chance for the MOSFETs of same leg turning ON simultaneously.

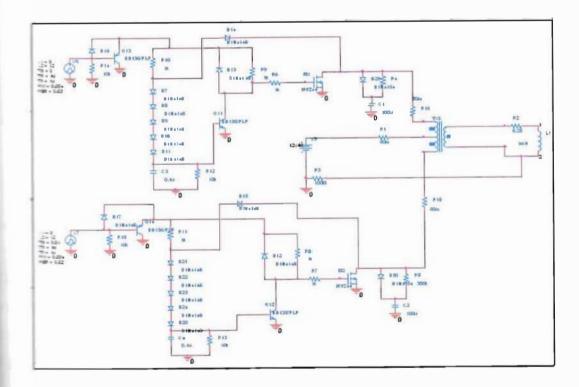

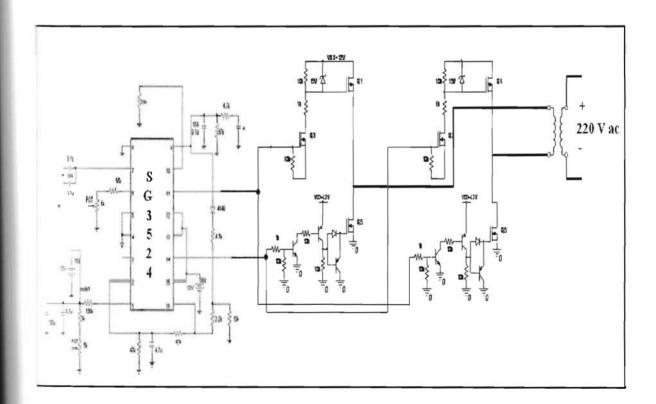

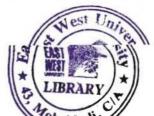

Fig 3.2(b) Schematic diagram of the inverter in method 1

e conduction of the H Bridge MOSFETs produces a 12V ac voltage at the output. The 12V voltage is fed into a step-up transformer to get a 220V ac voltage at the output of the sformer. A snubber circuit has been used in between the H-bridge and transformer inection. Due to several factors, the ac voltage at the input of the transformer does not main a constant 12V. Due to this variation, the voltage at the output of the transformer circuit is used from the solution to the input of the pulse generator i.e. SG3524.

e feedback is such that an opto-coupler (4N35) is connected from the transformer output to input pin (Vcc) of the pulse generator SG3524. The purpose of the opto-coupler is to late the pulse generator from the 220V high output stage as well as detect any variation in untput.

#### For method 2

SG3524 generates a 50Hz pulse which is to be supplied to the MOSFETs. The pulse uss out of two output pins of the SG3524, one 180deg shifted from the other.

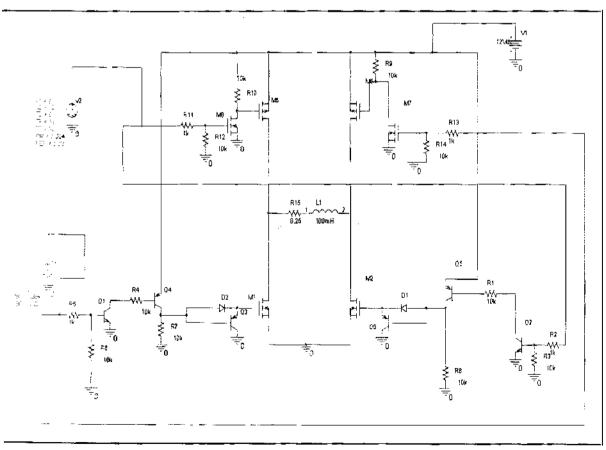

Fig 3.2(c) Schematic diagram of the inverter in method 2

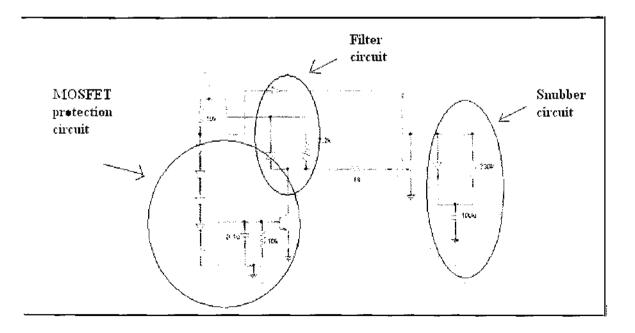

this configuration, a MOSFET protection circuit, a Snubber Circuit and a filter circuit is

## Fig: 3.2(d) Schematic Diagram of MOS Protection, Filter and Snubber circuit

before the pulse arrives at the MOSFET gate, it passes through a filter circuit where the width of the arriving pulse is reduced in order momentarily turn the MOSFET ON and OFF the nables smooth conduction.

After the MOSFET turns ON, a negative 12 volt appears across one coil of the transformer. a result of the voltage, a back emf is produced at the transformer coil which opposes the bitual polarity of the appearing voltage. To minimize the effect of this back emf, the Snubber actual is used. The Snubber circuit comprises of a diode and a resistor connected in parallel atd a capacitor connected in series with them. It is connected in such a way that when the situe emf is generated the diode is forward biased and the charge goes through it and gets atd in the capacitor. When the MOSFET is OFF, the capacitor discharges and neutralizes the back emf.

Inother stage is need for this operation, which is MOSFET protection circuit. This circuit is residually used to protect the MOSFET form abnormal voltage. The circuit contains an NPN insistor; the collector of the transistor is connected to the gate of the MOSFET switch. A tagacitor and a resistor are connected in parallel in the base of the transistor. Five diodes are included and connected in series with the parallel combination of capacitor and resistor. Here there diode is connected between the drain of the switch and the edge of the cascaded includes. When abnormal voltage appears the diode that connected between drain and cascaded includes, remains forward bias. And let the current flow the cascaded diodes. All the diodes are included a voltage is lower than 3V this series combination will never turns ON, and if it is the than 3V all diodes activates and charges the capacitor, which stores this voltage. If the include is significant NPN transistor remains ON and by force it OFFs the NMOS switch.

a called "power MOSFET choosing". This section highlights how a better power

b called "power MOSFET choosing". This section highlights how a better power

b called "power designed, which does not need any protection circuit during operation.

methods were constructed and after experimentation it was observed that method 1 method 2 there was no high side switching. Besides, in method 2 there was no high side so internal switching loss was comparatively less in method 2 than that of method method 2 was a better option in terms of efficiency as well as in terms of complexity. Tal hardware has been constructed following to method 2 and the design part will be

a ndiagly.

#### **3** Functional Description of parameters in Internal Blocks

## 3.1 SG3524 Square wave Generator

Fig 3.3.1(a) Top view of SG3524

SG3524 incorporate all the functions required in the construction of a regulating power may, inverter, or switching regulator on a single chip. They also can be used as the control ment for high-power-output applications. The SG3524 were designed for switching malators of polarity, transformer-coupled dc-to-dc converters, transformer less voltage rilers, and polarity-converter applications employing fixed-frequency, pulse-width aulation (PWM) techniques. The complementary output allows either single-ended or h-pull application. Each device includes an on chip regulator, error amplifier, mumable oscillator, pulse-steering flip-flop, two uncommitted pass transistors, a highcomparator, and current-limiting and shutdown circuitry [1].

#### metional block Diagram:

#### Fig 3.3.1(b) Functional Block Diagram of SG3524

#### **Principle of operation**

Find the provided externally by a resistor ladder network to provide a reference within the mon-mode range of the error amplifier or an external reference can be used. The output is two built-in transistors [2].

and 13 are the collectors of the transistors and pin 11 and 14 are the emitters. The of the transistors are internally connected to two 3 input NOR gates. One leg of each of a 1 input NOR gates are connected to the complimentary outputs of a T flip flop. Another

pin of each of the NOR gates are connected to comparator outputs, and another one is connected to an oscillator. Pin 4 and pin 5 are used to limit the current and protect against over load and over current. If no external reference is provided then the amplifier uses an internal reference. If the reference current crosses a particular limit, the SG3524 gets shut down automatically. Pin 10 is the shut down pin which is nothing but a common emitter NPN transistor. If the pin remains high the transistor is ON and shuts down the IC. And if low signal arrives at the pin, the output gets signal [2].

Pin 1 and pin 2 are the inputs of a P controller where pin 1 is a reference input and pin 2 is a feedback input. And the output of the P controller is pin 9.

is signal from CT is compared with the reference voltage to produce a pulse. The signal at the comparator output remains high, until the CT voltage is greater than the reference voltage, therwise it remains zero.

3524 is designed in such a way that two transistors remain ON in two different periods, rich makes an anti phase square output. The transistor gets ON if a high pulse arrives and a care wave at the output is obtained. One advantage of using SG3524 is the duty cycle of coutput can be varied.

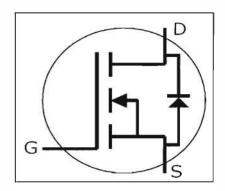

## 3.2 Introduction to Power MOSFET

SEET designed to handle significant power levels[5].

main advantages are[5]:

- i. high commutation speed

- ii. good efficiency at low voltages.

- iii. easy to drive (as it shares with the IGBT an isolated gate).

The power MOSFET is the most widely used low-voltage (i.e. less than 200 V) switch. It can be found in most power supplies, DC to DC converters, and low voltage motor controllers[5].

Fig3.3.2(a): Power MOSFET

Fig3.3.2(b): Power MOSFET symbol

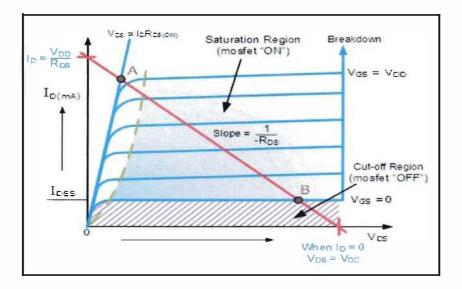

## Fig 3.3.2(c): IV characteristics of power MOSFET[6].

Every power devices has two kinds of breakdown states:

- i. primary breakdown

- ii. secondary breakdown.

Primary breakdown usually causes:

- 1. Over current

- 2. Over voltage

- 3. High temperature

For above mentioned problems, power MOSFET is preferable due to its average current sating. Power MOSFETs have no reverse bias junction, which means it enables over current protection or other way it can be said that it can take momentary or peak current. But COSFET is a voltage dependent device so its gate should be sealed [5].

OSFET does not have the secondary breakdown property because it does not have the reverse bias junction. As MOSFET has positive temperature coefficient so its temperature is coportional to the resistivity. As a result it will provide an automatic current spreading. Only unction based devices have the secondary breakdown property. As MOSFET is a junction the device it can be used in parallel [5].

#### Power MOSFET choosing

wer MOSFET is popular for use in switch-mode power supplies, power MOSFETs have rerating frequencies that are continuously being increased to reduce device size and increase wer density [19]. But it results a high di/dt, that make the negative effect stronger from trasitic inductance, and causes high-voltage spikes between the power MOSFET drain and urce during device turn-off. The spike is even worse during power up because of the empty k capacitors and the inductance on the transformer primary side being so low it almost unable the leakage inductance [19].

wadays robust design of power MOSFETs lets them resist of certain stress levels that minate the need for expensive protection circuits, if designers carefully analyze more parameters.

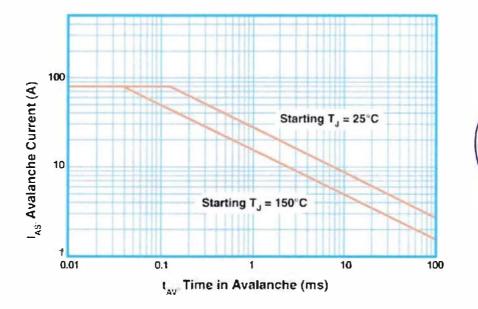

alanche-mode analysis and junction-temperature estimation are two practical and effective stods for choosing the optimal power MOSFET for switching power applications. Turing to apply these methods will, at the same time, give designers insight into the state balance between cost and reliability [19].

## Avalanche-mode analysis

In real applications, overvoltage conditions can be classified into two different groups. One condition is when the power MOSFET's drain-source voltage exceeds the absolute maximum specified, but lower than the device's breakdown voltage. Device then suitability can be determined through junction temperature analysis.

The second condition results when the device breaks down and goes into avalanche mode. During this stage drain-source voltage is clamped to its effective breakdown voltage and the current is commutated through a parasitic anti-parallel diode.

The breakdown occurs, device feasibility in any application is easy to determine using three simple parameters [19]. Those parameters are given as following:

\* The peak current through the power MOSFET during avalanche (IAS).

<sup>•</sup> The junction temperature (T<sub>J</sub>) at the start of the unclamped inductive switching (UIS) pulse.

\* The time the power MOSFET remains in avalanche  $(t_{AV})$ .

Designer can check the UIS capability of the device by plotting  $I_{AS}$  and  $t_{AV}$  on a graph for a given starting  $T_J$ . The plot is given below:

#### Fig 3.3.2(d) Avalanche mode Curve

In a power MOSFET's unclamped-inductive-switching (UIS) safe-operating-area (SOA) shaph, the safe operating area is below "Starting  $T_J = 150^{\circ}$ C" line while the area above the sharting  $T_J = 150^{\circ}$ C" line is beyond the devices rating. The area between the two lines requires special considerations [19].

There are three critical areas that known as the UIS safe operating area (SOA) are shown in the above figure:

below and to the left of the maximum junction temperature (150°C) line.

above and to the right of the 25°C line.

between the two lines.

Exercise 1 and 2 are easy to determine: either the device is within the UIS SOA rating (1), or reyond the rating (2). When the plot falls into area 3, it is necessary to calculate the junction emperature of the power MOSFET at the start of the UIS pulse to determine applicability.

his graph can also be applied to repetitive pulses through a superposition technique, wherein 4 UIS pulse is evaluated separately, as if it were a single pulse. Usually, the last pulse in a cries of power pulses occurs at the highest junction temperature and, thus, represents the orst stress. If the power MOSFET is within the UIS rating for the last pulse, it is certainly within the UIS ratings for previous pulses which occurred at lower junction temperatures [1].

## Estimating T<sub>i</sub>

SFET has a positive temperature co-efficient, so as temperature rises, a higher voltage is used to cause breakdown [19].

cording to the Fairchild data FQA11N90C 900-V MOSFET (MOSFET package) has a emperature coefficient of 1.02 V/°C, so at 120°C its BV<sub>DSS</sub> reaches about 990 V. In many weeks, the ambient temperature during MOSFET operation is over 25°C and the power loss

44

causes the junction temperature of the power MOSFET to rise above the ambient temperature.

In a real breakdown condition, the drain current reaches a much higher level and the breakdown voltage is even higher than the above value. For practical purposes, breakdown voltage in real applications is calculated at 1.3 times the rated low-current breakdown voltage [19].

Even though the abnormal voltage spike did not cause a device breakdown, the junction temperature of the power MOSFET should be kept below the specified maximum junction temperature to ensure reliability. The steady state junction temperature can be expressed as:

## $\mathbf{T}_{j} = \mathbf{P}_{\mathbf{D}} \mathbf{R}_{\mathbf{\theta} \mathbf{J} \mathbf{C}} + \mathbf{T}_{\mathbf{C}}$

where  $T_J$  is the junction temperature,  $T_C$  the case temperature,  $P_D$  the power dissipated in the unction, and  $R_{\Box JC}$  the steady-state thermal resistance between the junction and case of the -10SFET.

t our proposed methods, the power MOSFETs that have been used are:

- 1. IRF Z44 N Channel MOSFET

- 2. IRF 9520 P Channel MOSFET

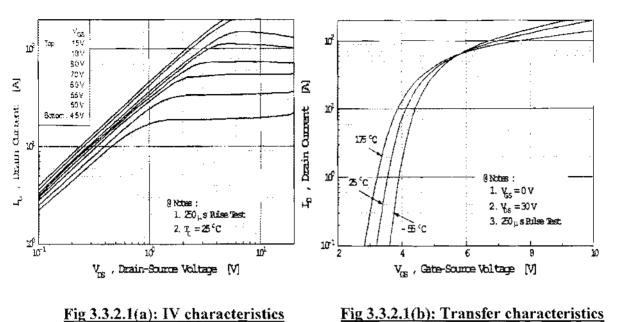

## 3.3.2.1 IRF Z44 N Channel MOSFET

RF Z44 is an advanced power MOSFET. It can handle current up to 50A and drain to source pltage up to 60V. IRFZ44 have the following features:

- Avalanched rugged technology.

- Rugged gate oxide technology.

- Low input capacitance

- Improved gate charge.

- Extended safe operating area.

- High operating temperature.

- Low leakage current: 10uA (MAX) at  $V_{DS} = 60V$ .

• Lower channel on resistance  $R_{DS(ON)} = 0.020\Omega$ .

## 3.3.2.2 IRF9520 P channel MOSFET

RF9520 P channel MOSFET is an advanced power MOSFET. It is designed for high power ripolar switching transistors which require high speed and low gate drive power. It can handle current up to 6A and drain to source voltage up to 100V. It requires a minimum channel on resistance of  $0.6\Omega[4]$ .

FF9520 has the following features:

- Designed, tested, and guaranteed to withstand a specified level of energy in the breakdown avalanche mode of operation.

- Single Pulse Avalanche Energy Rated.

- Nanosecond Switching Speeds.

- SOA is Power Dissipation Limited.

- Linear Transfer Characteristics.

- High Input Impedance.

#### 3.3.3 Driver circuit

the MOSFETs that have been used for switching are power MOSFETs, the driver circuits the been chosen in such a way that they can drive those power MOSFETs with ease.

## <u>Power-MOSFET gate driver</u>

Wer-MOSFET gate driver is a power amplifier that produces a high current gate drive for a over MOSFET from a low power input of a controller IC. It is required when a PWM outcoller cannot provide the output current required driving the gate capacitance a power obsFET. Gate drivers may be implemented as dedicated ICs, discrete transistors, or outsformers. Partitioning the gate-drive function off the PWM controller allows the output to run cooler and be more stable. It is done by eliminating the high peak currents to heat dissipation needed to drive a power MOSFET at very high frequencies [8].

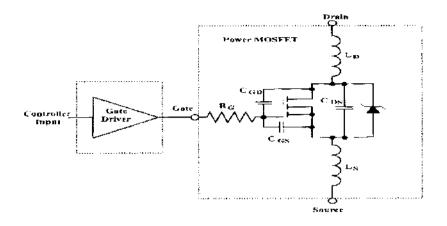

#### Fig: 3.3.3(a) Power MOSFET gate driver

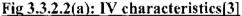

Fig 3.3.2.8: Equivalent circuit showing components that have greatest effect on switching.

A simplified model including the parasitic components that influence high-speed switching, gate-to-source capacitance (CGS), the gate-to-drain capacitance (CGD), and drain-to-source apacitance (CDS) is shown in the figure above. Values of the source inductance (LS) and drain inductance (LD) depend on the MOSFET's package. The other parasitic component is RG, the resistance associated with the gate signal distribution within the MOSFET that affects switching times [9].

In important attribute for the gate driver is its ability to provide sufficient drive current to taickly pass through the Miller Plateau Region of the power-MOSFET's switching transition. Miller Plateau Region: In the gate charge characteristics curve a flat horizontal portion is observed which the so called Miller Plateau Region). When the device switches, the gate Gtage is actually clamped to the plateau voltage and stays there until sufficient charge has seen added or removed for the device to switch. It is useful in estimating the driving -quirements, because it tells that the voltage of the plateau and the required charge to switch it device. Thus the actual gate drive resistor can be calculated, for a given switching time [1].

This region occurs when the transistor is being driven on or off, and the voltage across its  $\frac{1}{2}$  atte-to-drain parasitic capacitor (CGD) is being charged or discharged by the gate driver.

gure 2 plots total gate charge as a function of the gate-drive voltage of a power MOSFET.

#### Fig 3.3.3(b) Gate Charge vs Vgs of a Power MOSFET[10]

Driver circuit is also required because the Power MOSFET switches in their non conducting condition are subject to a spurious turn-on if the drain source voltage changes abruptly. These roltage variations usually occur in a very noisy environment. These spurious transitions are subject to both external circuit conditions and to parasitic elements of the MOSFET power switch itself. While an unwanted transition of the MOSFET from on-state to off-state may be damaging to the performance of the overall power system, a spurious transition from off-state on-state is frequently very severely damaging to the MOSFET power switch itself and in certain instances may cause its immediate destruction[7].

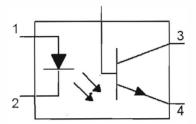

## 3.3.4 Optocoupler (4N35)

Optocoupler is basically an electronics device that isolates a particular side of the circuit from high or rapidly changing voltage side. Electronic equipment and signal and power transmission lines can be subjected to voltage surges induced by lightning, electrostatic discharge, radio frequency transmissions, switching pulses (spikes) and perturbations in power supply. In our proposed method, the 4N35 model has been used for the feed back stage.

#### Fig 3.3.4(a) Optocoupler

An optocoupler contains a LED and a phototransistor, a barrier is provided between LED and phototransistor so that the transistor and the LED can be isolated. LED and the transistor are separated so that light may travel across a barrier but not the electrical current. When an electrical signal is applied to the input of the optocoupler, its LED lights, and its light sensor then activates, this light emission turns ON the phototransistor and a corresponding electrical signal is generated at the output.

With a photodiode as the detector, the output current is proportional to the amount of incident light supplied by the emitter. The diode can be used in a photovoltaic mode or a photoconductive mode.

In photovoltaic mode, the diode acts like a current source in parallel with a forward-biased diode. The output current and voltage are dependent on the load impedance and light intensity.

In photoconductive mode, the diode is connected to a supply voltage, and the magnitude of the current conducted is directly proportional to the intensity of light.

nlike a transformer, the optocoupler allows for DC coupling and generally provides gnificant protection from serious overvoltage conditions in one circuit affecting the other.

## 4 Design Criteria

he specification of the inverter is given below:

| ower output   | 60 Watt      |

|---------------|--------------|

| utput voltage | 220 Volt A.C |

| put voltage   | 12 Volt D.C  |

| requency      | 50 Hertz     |

#### 4.1 Design of the Driver Stage

#### 4.1.1 Driver circuit for N channel MOSFET

#### or method <u>1</u>

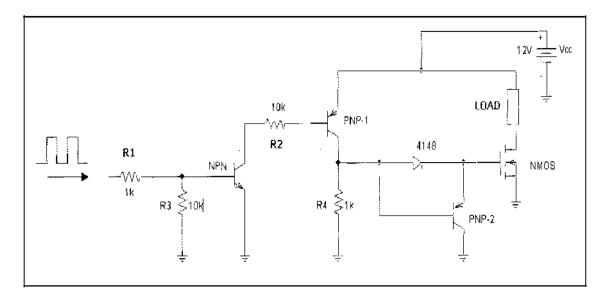

b construct the driver circuit for N channel MOSFET, one 4148 diode, two PNP and one PN transistors have been used. To bias the MOSFET properly, R3 and R1 have been placed scries which means a large portion of the supply voltage has been given at the gate of the IOSFET. This is because it is known that, with increment of gate to source voltage, drain to purce voltage will be lower which means the drop across the MOSFET will be minimum. A efficiently large resistance R2 has been connected from the collector to base of PNP-1 to andle large current. R4 has been used at the collector of PNP-1 to give the maximum eltage at the gate of the MOSFET [7].

#### Fig 3.4.1.1(a) Schematic Diagram of N Channel MOSFET Driver for method 1

While the positive pulse appears the NPN turns ON which eventually turns ON the PNP-1. As PNP-1 is turned ON, the power supply voltage appears at the gate of the MOSFET and turns it ON. The NPN transistor remains OFF while negative pulse appears. As a result the PNP-1 gets out of biasing condition. As the collector of the PNP-1 is connected to ground through a resistance so a negative voltage from ground appears at the gate of MOSFET which turns it OFF.

During the ON state time of MOSFET, a capacitance is formed due to the applied positive voltage to the gate which holds the voltage across it. At high frequency the MOSFET switches rapidly. Immediate after the positive pulse, when negative pulse appears the MOSFET does not turn OFF Instantly due to that capacitive effect which can be harmful for the device. To avoid that capacitive effect a PNP -2 transistor is used. This transistor is connected between the gate of the MOSFET and the ground. The base of PNP-2 is shorted to the collector of PNP-1. When the negative pulse appears immediate after the positive pulse, the PNP-2 gets ON and the storage charge that formed due the capacitance across the gate gets discharge instantly [7].

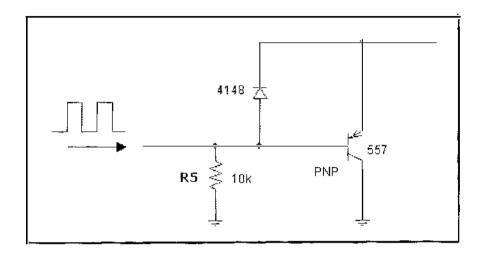

#### For method 2

For construction of the driver circuit for this method, two PNP and one NPN transistors have been used. R5 is chosen in such a way that during floating point, the negative through the R5 resistance turns the PNP ON and thus negative pulse reaches at the gate of the MOSFET which eventually turns it OFF.

#### Fig 3.4.1.1(b) Schematic Diagram for N Channel MOSFET Driver for method 2

While positive pulse appears the diode gets forward biased and the pulses makes its way to the gate of MOSFET and turn it ON. Immediate after that stage during floating point, the negative through the R5 reaches at the base of PNP which turns it ON and thus a negative rulse appears at the MOSFET gate and turns it OFF.

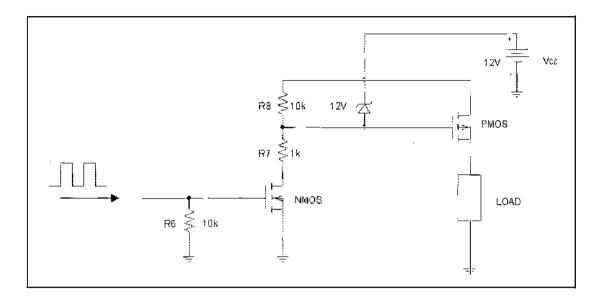

#### 3.4.1.2 Driver circuit for P channel MOSFET

To construct the driver circuit for P channel MOSFET, a 12 volts zener diode and an NMOS is needed. Actually, the NMOS controls the operation of PMOS here. R6 has been chosen in each a way to bias the NMOS properly. R7& and R8 has been connected in series. R7 usually - small value than R8 so that the NMOS can easily drive the PMOS. The zener diode has been placed in between supply voltage and gate of PMOS. It actually holds the 12 volt across : and maintains this voltage during supply voltage variation [12].

the principal application of the p-channel, enhancement mode POWER MOSFET is in witching power (or voltage) to grounded (ground return) loads. To drive the FET properly, the gate voltage must be referenced to its source. For enhancement-mode MOSFETs, this gate potential is of the same polarity as the MOSFET's drain voltage. To turn on, the nchannel MOSFET requires a positive gate-source voltage, whereas the p-channel MOSFET requires a negative gate-source potential. During switching, a MOSFET's source voltage must remain fixed, as any variation will modulate the gate and thus adversely affect performance. The circuit diagram is given below:

#### Fig 3.4.1.2(a) P Channel MOSFET Driver for method 1

From the above figure it is seen that the source of the NMOS is connected to the ground and the drain is connected to the gate of PMOS through a resistance. A resistance is connected from gate of the NMOS to ground. As the positive pulse occurs at the gate of NMOS it gets ON. For which a negative voltage appears to the gate of PMOS and turn it ON. When the negative pulse appears to the gate of NMOS it remains OFF, so the supply voltage comes across the gate of PMOS for which it remains OFF [12].

As method 2 has been selected for final hardware construction so the design of the driver stage is shown below in the figure:

## Fig 3.4.1.2(b) Schematic diagram of driver and power output stage

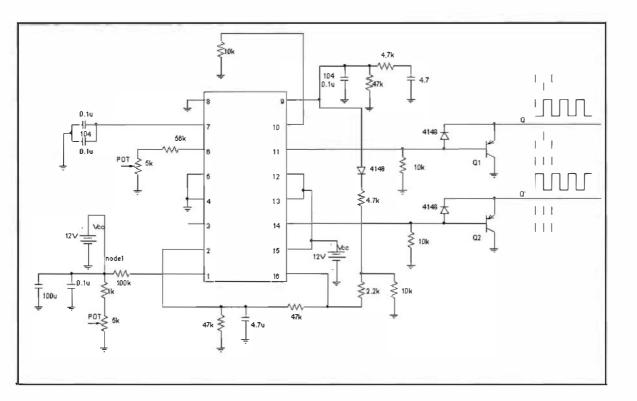

#### 3.4.2 Design of the 50 Hz Antiphase Square wave Generator

The oscillator control frequency of the SG3524 and is programmed by RT and CT as shown in the figure:

#### Fig 3.4.2(a) Schematic diagram of the frequency generator stage

Practical values of CT range from 0.001uF to 0.1uF. Practical values of RT range from 1.8k to 100k. This results in a frequency range from 130 Hz to 722 kHz.

As our motive is to supply a constant 50 Hz frequency from the pulse generator to the gate of the MOSFET for switching purpose, so we have chosen the value of RT and CT in such a way so that the frequency remains 50 Hz. The 50Hz generation process is described as following:

The collectors of two transistors are connected with Vcc. The 180 degree phase shifted outputs are taken from two emitters of the transistors. It is said in previous that a reference voltage is generated as power supply is concerned. Pin 7 and 6 generates the triangular wave signal. In pin 6 a resistor 56k is connected in series with a 5k variable POT. A stable 50Hz frequency can be obtained varying this POT. Pin 1 is used for adjusting duty cycle. A

resistance network is built in pin 1 as shown is the figure, two parallel capacitances are used in order to hold the terminal voltage. The supply voltage is divided in such a way that the maximum drop comes across the POT. Varying the POT duty cycle of the wave can be adjusted. Pin 9 is the output of comparator. The output of the comparator is connected to pin 16 with a resistance divider. Pin 16 is a reference voltage that is generated applying power supply. Now this voltage is divided with two 4.7k resistances and feedback to pin 2. Another 47uF capacitance is used to hold that terminal voltage. Pulse width would vary if the 5k POT get varied. Any change pin 1 voltage varies the POT fixes the pulse width.

#### 3.4.3 Design of the power output stage

The power rating is 60 watts and the output voltage is 220 volts.

Let the load is resistive, so the load current

$$I2 = \frac{60}{220} = 0.2727 \text{ A}$$

Let the transformer primary voltage is 12-0-12 volt and transformation ratio is

$$a = \frac{V1}{V2} = \frac{12}{220} = 0.0545$$

The corresponding primary current

$$II = \frac{I2}{a} = \frac{0.2727}{0.0545} = 5.004A = 5A$$

Fig 3.4.3(a) Schematic diagram of the power output stage

semiconductor switching device is needed which is able to carry this 5A current. IRFZ44 and IRF9520 are the suitable devices for that. The ratings of these devices are discussed in revious sub-sections. The connections of these devices have been shown in the above figure. Now, as 5A current is flowing through the drain of the MOSFET. So, from the equation of rain current (in linear region),

$$I(\text{linear}) = \mu \operatorname{Cox} \frac{W}{L} \times \{(\text{Vgs-Vt}) \text{ Vds}\} - \frac{V^2}{2} \dots \dots \dots (\text{xiii})$$

rom the above equation, assuming the value of Vds small as the switching loss is very low coording to our design. Then the square term can be neglected. Now, taking a constant value f conduction parameter, threshold voltage, the value of Vgs can be obtained which is ufficiently a large value.

he square wave generator stage is not able to carry this amount of voltage. So, multiple age amplification is required.

## 3.4.4 Total Harmonic Distortion (THD) analysis

The equation of total harmonic distortion is given below:

$$THDv = \frac{\sqrt{\sum_{n=2}^{\infty} (V_{RMS})^2 - (V_{1,RMS})^2}}{V_{1,RMS}} \quad \dots \dots \dots (xiv)$$

From the simulation the fundamental peak is obtained approximately 10.80V for first method. And for second method it is about 9 V.

Therefore, THD for the first method is =

$$\frac{(V_s^2 - V_{1rms}^2)^{0.5}}{V_{1rms}^2}$$

$$= 0.4843$$

$$= 48.43\%$$

THD for the second method is  $= \frac{(V_s^2 - V_{1rms}^2)^{0.5}}{V_{1rms}^2}$ = 0.8819= 88.19%

So the above calculation states that method 1 gives a better THD response. Huge amount of harmonics occurs for second method. It can be said that, there'll be less harmonic distortion for method 1.

## 3.4.5 Selection of the output Transformer

In this project we have used a 12-0-12 transformer. Which means it is a center tapped transformer with three phase input. And it has current ratings of 6A.

In this section a brief discussion is done regarding transformer. This section highlights the improvement that can be done to design a transformer. This will result a decent construction of a single phase inverter. A transformer will provide best characteristics when the primary coil that takes over magnetization of the iron core fits closely around the core [2]. In this project transformer would be the 220 Volts coil, on our inverter however it will be the 12 volt coil.

The main objective is to choose the number of turns so that the desired voltage could generate.

For the computation of the numbers of turns the following consideration applies:

#### **Computation**

We specify the maximum magnetic induction on a value of 1.5 Tesla [2]. For computation now only two simple equations are necessary:

- 1.  $U_{ind} = n \times F / t \dots (xv)$

- $n=U_{ind} x t/F$

- 2.  $F = B \times A \dots (x \vee i)$

| U <sub>ind</sub> =induced voltage | n=number of turns                        |

|-----------------------------------|------------------------------------------|

| F = magnetic flux                 | t=transistor switch-on time              |

| B= magnetic induction             | A=cross-section area of transformer core |

For power electronics resistive load shall not calculate on energy conversion. Thus the whole Dattery voltage will apply on the transformer coil for the whole switch-on time of the Transistor. The switch-on time results in 5 milliseconds; depended on the period of the 50 cycles / second oscillation and a duty-cycle of 25% (period of a 50 cycle oscillation is 1 / 50 Hz = 20 milliseconds).

These calculations are done for 60 VA transformers.

At low frequency such as 50-120Hz should use laminated core

Let the cross-section area of the transformer calculates to A = 60 mm x 80 mm = 4,8 x  $10^{-3}$  m<sup>2</sup> [2].

$U_{ind} = 12$  Volt B= 1.5 Tesla = 1.5 Vs/m<sup>2</sup>

A = 5 ms  $A = 4.8 \times 10^{-3} m^2$

With equation 2 magnetic flux calculates to  $F = B \times A = 1.5 \text{ Vs/ } \text{m}^2 \times 4.8 \times 10^{-3} \text{ m}^2 = 7.2 \times 0^{-3} \text{ Vs}$

Now the value of F is being set in equation 1.

Number of turns on primary  $N_P = U_{ind} \times t/F = 12 \ V \times 5 \times 10^{-3} \ s / (7.2 \times 10^{-3} \ Vs) = 8.33$  rounded up 9 turns).

Number of turns on secondary  $N_S = U_{ind} \times t/F = 220V \times 5 \times 10^{-3} \text{ s} / (7.2 \times 10^{-3} \text{ Vs}) = 152.78$ rounded up 153 turns).

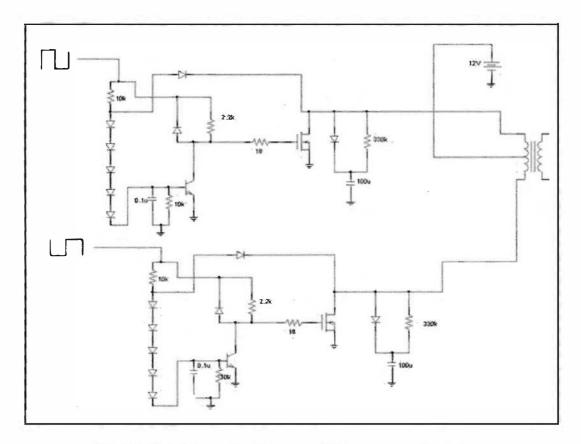

## .4.6 Design of the Feed Back Stage

he circuit for feedback stage is given below:

bove figure is proposed for feedback output stage. In this project the feedback stage is not onstructed practically. This is a proposal that can be applied as a feedback stage.

eedback circuit contains an optocoupler. The voltage that is obtained to the output is beedback to the comparator of SG-3524 through optocoupler. Optocoupler isolates the pulse eneration circuit, apart from high side. 220V output voltage passed through a full bridge. So unidirectional AC voltage can be obtained. If AC voltage is applied to the optocoupler input, then the diode within the optocoupler remains forward bias only for half cycle. It will emain OFF for the negative cycle. That's why a bridge is used here. When the corresponding urrent of 220v goes from the internal diode of optocoupler, it induces a minimum voltage rop of 0.7V across it and generates a light. This lighting turns on the photo transistor, which makes the collector and emitter short. The collector was biased with the supply voltage. Therefore supply voltage goes to the resistance divider terminal as shown in above figure, and the pulse width get adjusted by the POT in order to generate anti phase 50Hz square as escribed in previous section.

## Construction and Testing

## .1 Construction

e different block designs discussed previously in this chapter were constructed in Vero rd. Each block after construction was tested individually.

## .2 <u>Testing</u>

following tests are made for calculating the performance of designed inverter.

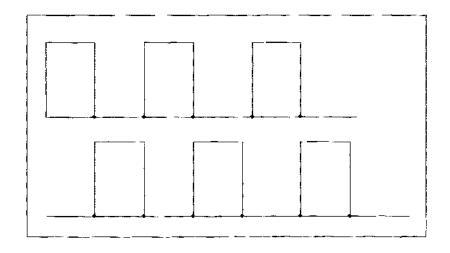

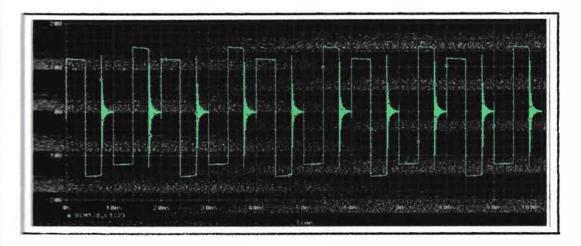

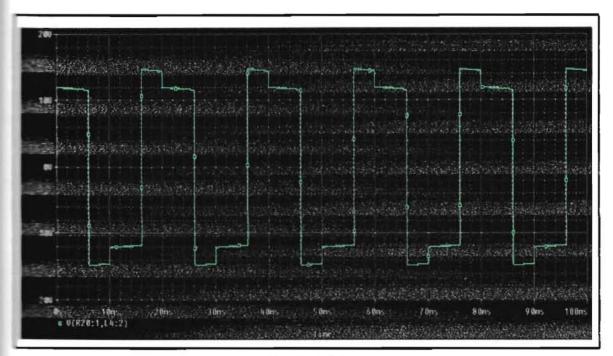

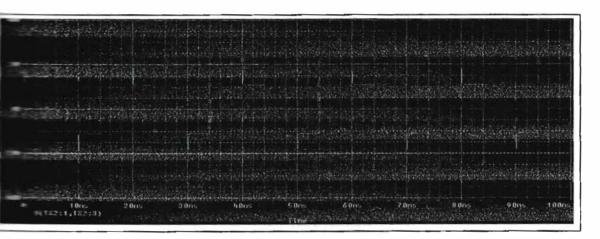

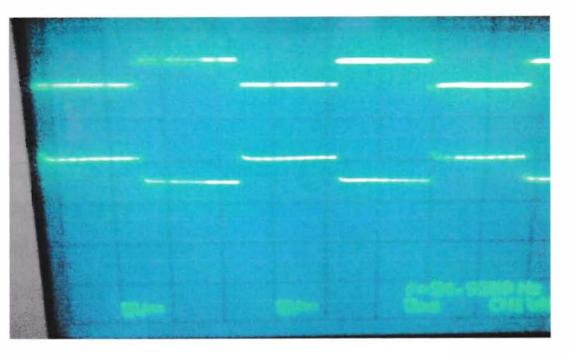

## .2.1 Output Wave shape of Square wave Generator

ording to the design, the output should be two antiphase square waves of 50 Hz, having volt peak.

photograph is shown below, is taken from an oscilloscope screen, when the oscilloscope onnected to the output of the stage.

Fig 3.5.2.1(a) Square Wave Generation from SG3524

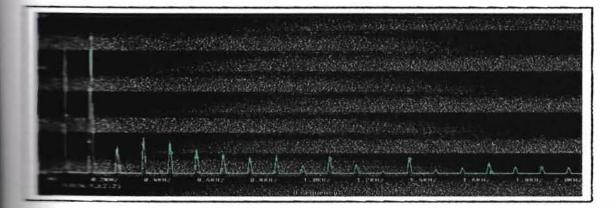

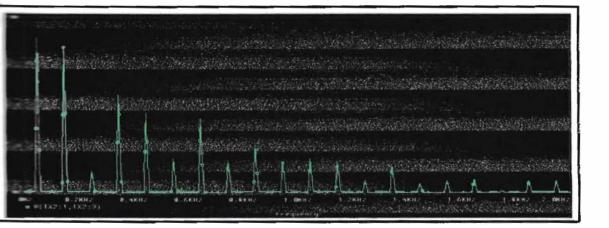

## .2.2 Voltage Wave shapes of transformer Primary

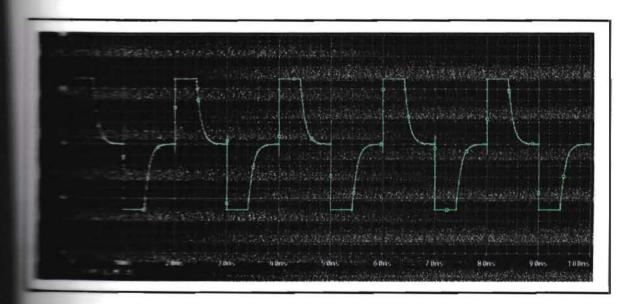

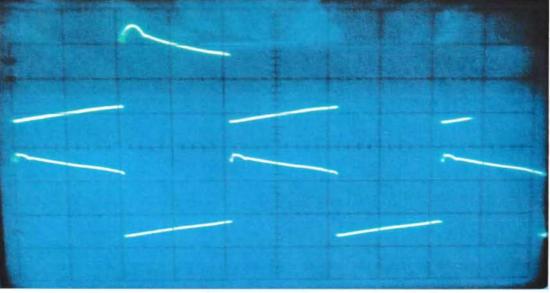

#### method 1

Primary voltage wave shape at no load

Fig 3.5.2.2(a)

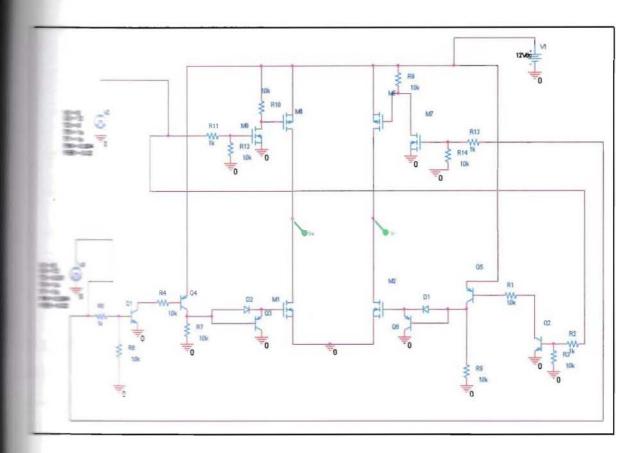

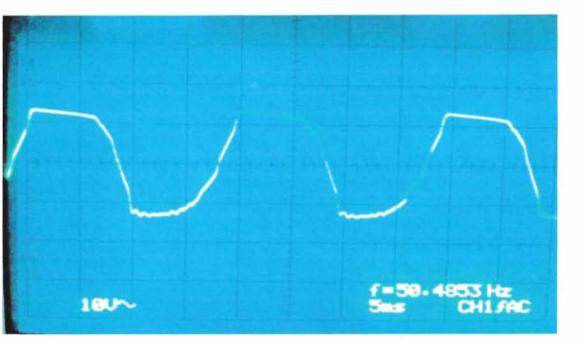

## For method 2

The voltage wave shapes of transformer primary and secondary are shown below

(b) Primary voltage wave shape at no load

Fig 3.5.2.2(b)

- (c) Secondary voltage wave shape at 60W load

Fig 3.5.2.2(c)

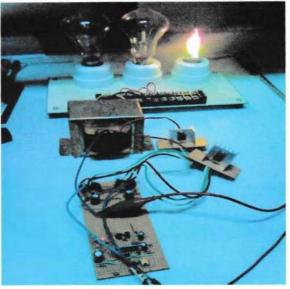

## 3.5.2.3 Constructed Single Phase Inverter

Fig 3.5.2.3(a) Inverter Hardware

Fig 3.5.2.3(b) Inverter with 5W load

Fig 3.5.2.3(c) With 60 watt load

Fig 3.5.2.3(d) Wave shape at 60W load

n the above table, it can be observed that the experimental values are more or less similar the theoretically calculated values. Due to some internal losses in the transformer coils and r parameters like diodes, transistors, the obtained output power differ a little than the red quantity which is in suitable range.

## **Conclusion**

inverter was constructed and tested and found to work satisfactory with operating input age of 12V. The output voltage of this inverter is almost constant at given load. The erimental input and output wave shapes matches the computer simulated wave shapes.

# CHAPTER 4 TECHNIQUE OF IMPROVEMENT IN EFFICIENCY

#### 4.1 Introduction

Efficiency, literally, means the capability of a specific application of effort to produce a desired outcome by wasting the minimum amount of effort. In engineering terms, it can be said that efficiency is the ratio of a machine's energy output to the energy input.

For an inverter, we can say that efficiency is the percentage of power that goes into the inverter and comes out as useable AC current. In our proposed project, we emphasized more on the inverter efficiency. Our effort was to reduce the internal loss of the circuit of the inverter and get the maximum output power.

#### 4.2 Proposed Technique for Improved Efficiency

The operation of our proposed inverter is mainly based on the switching of MOSFETs. In a conventional inverter built nowadays, the switching is done using only N-type MOSFETs. The reason of using NMOS is that it gets less heated while switching. But on the other hand the efficiency is being compromised using only NMOS. This is because we experimented our proposed inverter using only NMOS and found that during positive switching, NMOS does not function properly. There is a noticeable voltage drop, i.e. around 3V across the NMOS. As a result, the desired output was not obtained at no load. Due this significant drop across NMOS at high side, full conduction is not possible at no load output and thus the internal loss increases and the output power is not as desired. Thus in our proposed inverter, we have implemented two methods.

#### For method 1

In our proposed inverter, we used PMOS for the positive or high side switching and NMOS for the negative or low side switching. The advantage of using PMOS in high side switching is that the voltage drop across the PMOS while switching is very low i.e. 0.3V compared to the NMOS's 3V. Also, using NMOS for low side switching gives us a smooth conduction with a very less voltage drop. As a result, using this arrangement, we were successful at reducing the internal loss of the inverter and get almost full conduction from the MOSFETs.

#### For method 2

In this method, we used no switching in the positive or high side. The supply voltage from the battery had been directly connected to the one terminal of the transformer. As a result, there was no switching loss at the positive or high side. Besides, using NMOS in negative side provides smooth conduction due to the high mobility of electrons in it. So, this arrangement was more beneficial to reduce internal loss and increase efficiency.

After experimenting both the methods, it was observed that method 2 was much better than method 1 in terms of efficiency. Besides, some complexities were also observed in method 1 during positive switching. So, after experimentation, method 2 was found to be a better one and had been finalized for the final hardware construction.

#### 4.3 Implementation and Outcome

#### <u>Method 1</u>

At no load, we achieved the output voltage of 10.63V by giving an input of 12V. So, by using PMOS for high side switching and using NMOS for low side switching, we were able to increase the inverter efficiency.

Efficiency =

$$\frac{output \ voltage}{input \ voltage} X \ 100 \%$$

=  $\frac{11.3}{12} X \ 100\%$

= 94.17 %

#### Method 2

At no load, we achieved the output voltage of 11.6V by giving a 12V input. So, by switching only the negative side and connecting the positive side directly to the transformer, we were able to achieve an even better efficiency compared to the previous method.

Efficiency =

$$\frac{output voltage}{input voltage} X 100 \%$$

=  $\frac{11.6}{12} X 100$

= 96.67 %

From the above two calculation it is obvious that method 2 has much better efficiency than method 1. So, it can be said that the experiment for improving efficiency by reducing internal loss was a success

#### 4.4 Conclusion

One of the prior concerns during construction of the inverter was the efficiency. That is why, two methods were put into operation and the better solution in terms of efficiency was finally constructed. The notion was to improve the efficiency by reducing the internal switching loss.

## CHAPTER 5 SUMMARY, CONCLUSION AND RECOMMENDATIONS

#### Summary

single phase inverter under fixed output voltage is designed and constructed in this project. chapter-1, introductory discussion, proposed method and scope of the project is discussed. nciple of operation, modulation technique is discussed and computer analysis is done in apter-2. In Chapter 3, details design procedure; construction and testing are discussed and died. Chapter 4 includes discussion on efficiency and the techniques to improve it.

## Conclusion

e output voltage of this single phase inverter is square wave. The square wave sometimes kes problems in reactive circuits. It restrains several harmonics, which causes heating. But the important benefits of square wave are that its peak value is constant with respect to ne. To operate a transistor at a definite voltage, the square wave does not take any time ereas the sine wave takes some time for the transition to the peak.